สิ่งที่ต้องมี

1. Read this “ISE_10 Start Verilog.pdf”

2. Read

this “ISE 11_1 Encoder Tutorial - VHDL Verilog.pdf”

Digital

1.

ใช้ Xilinx

ISE 14.4 ด้วยโปรแกรม VHDL ในการสร้าง 2

to 4 Line Encoder

ขั้นตอนดำเนินงานด้วย

ISE 14.2

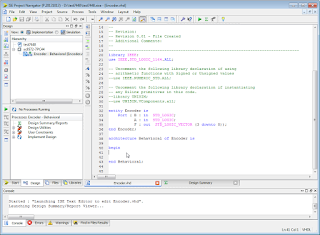

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity Encoder is

Port ( B : in STD_LOGIC;

A : in STD_LOGIC;

F : out STD_LOGIC_VECTOR (3 downto 0));

end Encoder;

architecture Behavioral of Encoder is

begin

F <= "0001" when (B='0' and A='0') else

"0010" when (B='0' and A='1') else

"0100" when (B='1' and A='0') else

"1000" ;

end Behavioral

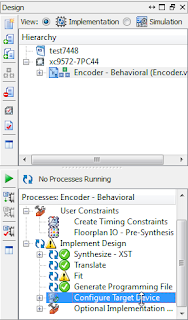

ขั้นตอนการดำเนินงานด้วย ISE 14.2

New Project

Family

XC9500 CPLDs

Device

XC9572

Package

PC44

New Source

B

in

A

in

F

out þ

3 0

Inplement All

|

Assigned Pin

Inplement All

Lode

Program

|

Select file XXXX.jed

Opertation à Program

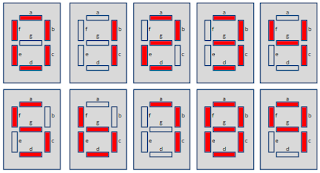

2.

ใช้ Xilinx

ISE 14.4 ด้วยโปรแกรม VHDL ในการสร้าง 7_Segment

Encoder

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

-- Uncomment the following library declaration if

using

-- arithmetic functions with Signed or Unsigned values

--use IEEE.NUMERIC_STD.ALL;

-- Uncomment the following library declaration if

instantiating

-- any Xilinx primitives in this code.

--library UNISIM;

--use UNISIM.VComponents.all;

entity Encoder is

Port ( Inport : in STD_LOGIC_VECTOR (3 downto

0);

Outport : out STD_LOGIC_VECTOR (6 downto 0));

end Encoder;

architecture Behavioral of Encoder is

begin

Outport <=

"1111110" when Inport ="0000" else

"0110000" when Inport

="0001" else

"1101101" when Inport

="0010" else

"1111001" when Inport

="0011" else

"0110011" when Inport

="0100" else

"1011011" when Inport

="0101" else

"1011111" when Inport

="0110" else

"1110000" when Inport

="0111" else

"1111111" when Inport

="1000" else

"1111011" when Inport

="1001" else

"1110111" when Inport

="1010" else

"0011111" when Inport

="1011" else

"1001110" when Inport

="1100" else

"0111101" when Inport

="1101" else

"1001111" when Inport

="1110" else

"1000111" ;

end Behavioral;

3.

จากโปรแกรมนับขึ้น 4 บิตด้วย VHDL

ทดสอบกับ LED Logic Monitor 4 ดวง

ให้ปรับปรุงโปรแกรมนี้เพื่อนับแบบเลข 8 บิต ทดสอบร่วมกับ 7_Segment Encoder

ที่สร้างขึ้นจากข้อ 2 การแสดงผลจะเริ่มจาก 00 – FF

VHDL Code - 4Bit Up Counter from

0000 to 1111

library

ieee;

use

ieee.std_logic_1164.all;

use

ieee.std_logic_unsigned.all;

entity

Counter is

Port

( clk : in STD_LOGIC;

reset

: in STD_LOGIC;

Output

: out STD_LOGIC_VECTOR (3 downto 0));

end

Counter;

architecture

Behavioral of Counter is

signal

pre_count: std_logic_vector(3 downto 0);

begin

process(clk,

reset)

begin

if

reset = '1' then

pre_count

<= "0000";

elsif

(clk='1' and clk'event) then

pre_count

<= pre_count + "1";

end

if;

end

process;

Output

<= pre_count;

end

Behavioral;

VHDL Code – 8Bit Counter from 00 to

FF

#include <SPI.h>

#include "LedMatrix.h"

#include <Wire.h>

#include

"ClosedCube_HDC1080.h"

#define NUMBER_OF_DEVICES 1

#define CS_PIN D8

LedMatrix ledMatrix =

LedMatrix(NUMBER_OF_DEVICES, CS_PIN);

//Button D3

//SDA in HDC1080 D2

//SCl in HDC1080 D1

//CLK in MAX7219 D5

//DIN in MAX7219 D7

//CS in MAX7219 D8

ClosedCube_HDC1080 hdc1080;

void setup() {

pinMode(D3, INPUT_PULLUP);

Serial.begin(115200); // For debugging output

ledMatrix.init();

ledMatrix.setIntensity(15); // range is 0-15

ledMatrix.clear();

ledMatrix.commit(); // commit send buffer to the displays

Serial.begin(9600);

Serial.println("ClosedCube HDC1080 Arduino Test");

hdc1080.begin(0x40);

Serial.print("Manufacturer ID=0x");

Serial.println(hdc1080.readManufacturerId(), HEX); // 0x5449 ID of Texas

Instruments

Serial.print("Device ID=0x");

Serial.println(hdc1080.readDeviceId(), HEX); // 0x1050 ID of the device

}

int stat = 1;

void loop() {

ledMatrix.clear();

ledMatrix.commit(); // commit send buffer to the displays

Send2MAX7129(4, 5, 0);

Send2MAX7129(3, 6, 0);

Send2MAX7129(2, 7, 0);

Send2MAX7129(1, stat, 0);

stat++;

if(stat==5){

stat=1;

}

delay(1000);

}

//===================================================

// ##SegPosition >> 87654321 ##SegData >> tabcdefg

//===================================================

void Send2MAX7129(byte SegPosition,

byte Value, bool dotDigit) {

const static byte charTable [] =

{ B01111110, B00110000, B01101101, B01111001, //

B00110011, B00001110, B01001111, B00111101

};

Value = charTable[Value];

if (dotDigit == 1) Value |= 0x80;

digitalWrite(CS_PIN, LOW);

SPI.transfer (SegPosition);

SPI.transfer (Value);

digitalWrite (CS_PIN, HIGH);

}

//===================================================

// ##SegPosition >> 87654321 ##SegData >> tabcdefg

//===================================================

void SendData2MAX7129(byte

SegPosition, byte SegData) {

digitalWrite(CS_PIN, LOW);

SPI.transfer (SegPosition);

SPI.transfer (SegData);

digitalWrite (CS_PIN, HIGH);

}

4.

ปรับวงจรนับเป็น Up-Down

Counter 4 bit โดยมี สัญญาญ CU ควบคุมการนับ ทดสอบร่วมกับ

7_Segment Encoder ที่สร้างขึ้นจากข้อ 2 การแสดงผลระหว่าง 0

- F

·

C ควบคุมการนับและหยุดนับ ถ้าเป็น 1

ให้นับต่อ ถ้าเป็น 0 ให้หยุดนับ

·

U ควบคุมทิศทางการนับ ถ้าเป็น 1 ให้นับขึ้น ถ้าเป็น 0

ให้นับลง

VHDL

Code - 4Bit Counter with Control (0000 - 1111)

library ieee;

use ieee.std_logic_1164.all;

use

ieee.std_logic_unsigned.all;

entity Counter

is

Port

( Clk :

in STD_LOGIC;

Enable :

in STD_LOGIC;

UpDown :

in STD_LOGIC;

Reset :

in STD_LOGIC;

Output :

out STD_LOGIC_VECTOR (3 downto 0));

end Counter;

architecture

Behavioral of Counter is

signal

pre_count: std_logic_vector(3 downto 0);

begin

process(Clk,

Reset, Enable, UpDown)

begin

if

Reset = '1' then

pre_count

<= "0000";

elsif

(Clk='1' and Clk'event) then

if

Enable='1' then

if

UpDown='1' then

pre_count

<= pre_count + "1";

else

pre_count

<= pre_count - "1";

end

if;

end

if;

end

if;

end

process;

Output

<= pre_count;

end Behavioral;

VHDL Code – 4Bit Counter from 0 to F

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity Counter is

Port

( Clk : in

STD_LOGIC;

Enable : in STD_LOGIC;

UpDown : in

STD_LOGIC;

Reset

: in STD_LOGIC;

Output : out STD_LOGIC_VECTOR (6 downto 0));

end Counter;

architecture Behavioral of Counter

is

signal pre_count:

std_logic_vector(3 downto 0);

begin

process(Clk,

Reset, Enable, UpDown)

begin

if

Reset = '1' then

pre_count

<= "0000";

elsif

(Clk='1' and Clk'event) then

if

Enable='1' then

if

UpDown='1' then

pre_count

<= pre_count + "1";

else

pre_count

<= pre_count - "1";

end

if;

end

if;

end

if;

end

process;

Output

<= "1111110" when pre_count

="0000" else

"0110000"

when pre_count ="0001" else

"1101101"

when pre_count ="0010" else

"1111001"

when pre_count ="0011" else

"0110011"

when pre_count ="0100" else

"1011011"

when pre_count ="0101" else

"1011111"

when pre_count ="0110" else

"1110000"

when pre_count ="0111" else

"1111111"

when pre_count ="1000" else

"1111011"

when pre_count ="1001" else

"1110111"

when pre_count ="1010" else

"0011111"

when pre_count ="1011" else

"1001110"

when pre_count ="1100" else

"0111101"

when pre_count ="1101" else

"1001111"

when pre_count ="1110" else

"1000111"

;

end Behavioral;

|

5.

ออกแบบ ALU(Arithmetic

Logic Unit) โดยใช้ VHDL ให้มี Output

F[3..0] และ Input A[1..0], B[1..0], C[2..0] กำหนดฟังก์ชันการทำงาน

ดังนี้

C[2..0]

|

Logic

Function

|

C[2..0]

|

Math

Function

|

|

000

|

F= A

|

100

|

F = A plus

B

|

|

001

|

F = A OR

B

|

101

|

F = A minus

B

|

|

010

|

F = A AND

B

|

110

|

F = -A

|

|

011

|

F = A XOR

B

|

111

|

F = A plus

1

|

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

Use ieee.std_logic_unsigned.all;

Use ieee.std_logic_arith.all;

use IEEE.NUMERIC_STD.ALL;

Use ieee.std_logic_unsigned.all;

Use ieee.std_logic_arith.all;

use IEEE.NUMERIC_STD.ALL;

entity Sample5 is

Port ( C : in STD_LOGIC_VECTOR (2 downto 0);

iA : in STD_LOGIC_VECTOR (1 downto 0);

iB : in STD_LOGIC_VECTOR (1 downto 0);

F : out STD_LOGIC_VECTOR (3 downto 0));

end Sample5;

Port ( C : in STD_LOGIC_VECTOR (2 downto 0);

iA : in STD_LOGIC_VECTOR (1 downto 0);

iB : in STD_LOGIC_VECTOR (1 downto 0);

F : out STD_LOGIC_VECTOR (3 downto 0));

end Sample5;

architecture Behavioral of Sample5 is

signal pre: std_logic_vector(3 downto 0);

signal InA: std_logic_vector(3 downto 0);

signal InB: std_logic_vector(3 downto 0);

signal pre: std_logic_vector(3 downto 0);

signal InA: std_logic_vector(3 downto 0);

signal InB: std_logic_vector(3 downto 0);

begin

InA(1 downto 0) <= IA(1 downto 0);

InB(1 downto 0) <= IB(1 downto 0);

process(C,IA,IB)

begin

if(C="000") then pre <= not InA;

elsif(C="001") then pre <= InA or InB;

elsif(C="010") then pre <= InA and InB;

elsif(C="011") then pre <= InA xor InB;

elsif(C="100") then pre <= InA + InB;

elsif(C="101") then pre <= InA - InB;

elsif(C="110") then pre <= (not InA)+1;

else pre <= InA + 1;

end if ;

InA(1 downto 0) <= IA(1 downto 0);

InB(1 downto 0) <= IB(1 downto 0);

process(C,IA,IB)

begin

if(C="000") then pre <= not InA;

elsif(C="001") then pre <= InA or InB;

elsif(C="010") then pre <= InA and InB;

elsif(C="011") then pre <= InA xor InB;

elsif(C="100") then pre <= InA + InB;

elsif(C="101") then pre <= InA - InB;

elsif(C="110") then pre <= (not InA)+1;

else pre <= InA + 1;

end if ;

end process;

F <= pre;

end Behavioral;

F <= pre;

end Behavioral;

ไม่มีความคิดเห็น:

แสดงความคิดเห็น